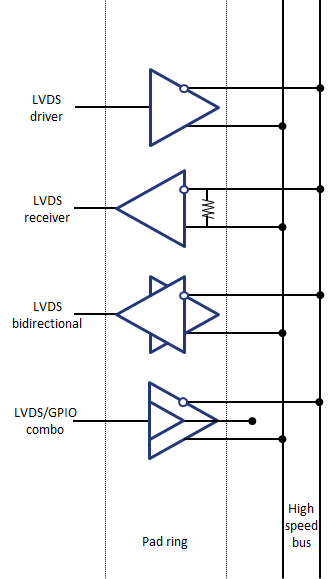

LVDS IO cells library

Description:

The nSIO_TS65GP_2V5_1V0 library is an IO cells library combining various LVDS and general purpose I/O powered at 2.5V/1.0V or 1.8V/1.0V, designed on the TSMC 65 GP technology. The library is composed according to the customer’s choice of cells.

Applications:

Multi-purpose reconfigurable IO

Point-to-point, point-to-multipoint or bus-based IC high-speed data communications

Intra-package (e.g. MCM or SIP) inter-die high-speed data communications

Backplane high-speed data communications

High-speed serial communications (HDMI, SATA, PCIeX, etc.)

Communication to LCD/OLED screens

Video sensor digital data interface

Main features:

Standard-compliant to TIA/EIA-644-A-2001

Built-in, low parasitic ESD protection

Easily integrates with TSMC I/O library cells

All-in-ring® topology, so no core silicon area is used by LVDS

The same cells operate with 2.5V/1.1V or 1.8V/1.1V power supplies

Standby/power down mode

Digital loopback functions to ease ATE testing

Up to 2 Gbps data rate LVDS

Product brief:

Main characteristics:

2.5V/1.0V IO/Core transistor

Fully compliant with TIA/EIA-644-A-2001

TSMC 65 GP

Deliverables:

GDS II layout

LEF abstract

CDL netlist

Liberty timings

Verilog description

A full datasheet

An integration note

Status:

Silicon proven

Radiation proven:

No

Automotive grade:

No